在人工智能与异构计算时代,处理器芯片已形成"通用+领域专用"的生态矩阵。本文通过对比CPU、GPU、NPU、DPU、TPU、IPU、LPU、MCU、MPU九类芯片,揭示其技术特性与协同关系。

一、芯片类型核心对比矩阵

| 芯片类型 | 全称 | 核心设计目标 | 关键架构特征 | 典型应用场景 |

|---|---|---|---|---|

| CPU | 中央处理器 | 通用任务处理 | 多级流水线/超标量架构,强分支预测能力 | 操作系统/应用程序运行 |

| GPU | 图形处理器 | 并行计算加速 | 数千计算核心,SIMD/SIMT架构 | 图形渲染/深度学习训练 |

| NPU | 神经网络处理器 | 神经网络加速 | 矩阵计算单元,支持稀疏化计算 | 图像识别/语音处理 |

| DPU | 数据处理器 | 数据面处理卸载 | 网络协议硬件解析+加解密引擎 | 云计算网络虚拟化 |

| TPU | 张量处理器 | 张量运算优化 | 脉动阵列设计,混合精度计算支持 | 谷歌AI训练与推理 |

| IPU | 智能处理器 | 图计算加速 | MIMD架构,大规模片上SRAM | Graphcore的图神经网络加速 |

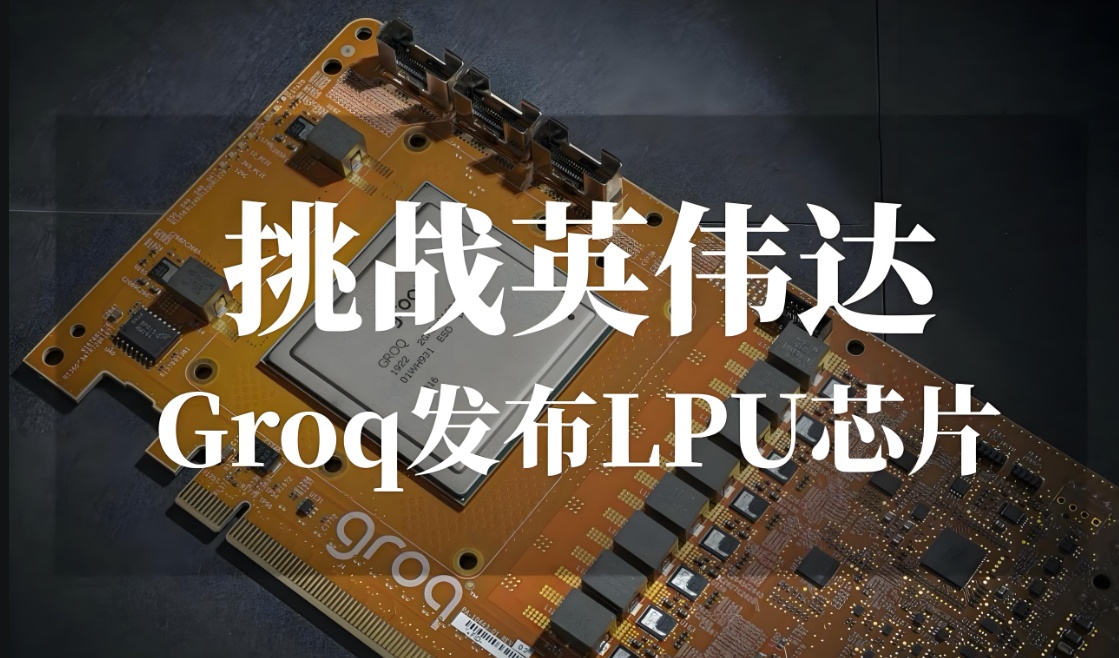

| LPU | 语言处理单元 | 大语言模型推理 | 超长上下文窗口支持,低延迟token生成架构 | ChatGPT类对话系统 |

| MCU | 微控制器 | 嵌入式控制 | 集成存储/外设,低功耗设计 | 家电控制/传感器管理 |

| MPU | 微处理器 | 高性能嵌入式计算 | 多核架构,外接高速存储 | 工业机器人/智能网关 |

二、关键技术差异分析

1. 计算架构创新

-

并行粒度

-

CPU:指令级并行(ILP)+多线程(4-128线程)

-

GPU:数据级并行(DLP)+线程级并行(TLP,百万线程)

-

LPU:序列级并行(SLP),支持512k+ tokens上下文处理

-

-

内存系统

-

GPU:HBM3显存(>1TB/s带宽)

-

LPU:上下文专用缓存(处理长文本序列)

-

IPU:300MB片上SRAM(减少片外访问)

-

-

能效比对比

(NPU在AI推理任务中能效可达CPU的100倍)

2. 专用指令集演进

-

通用指令集:x86/ARM提供完整运算与控制指令

-

领域指令集:

-

TPU:矩阵乘加指令(MXU)

-

LPU:注意力机制硬件指令(如FlashAttention加速)

-

DPU:RDMA数据搬运指令

-

三、功能定位的协同与竞争

共同特征

-

物理基础:均采用先进制程(3nm-28nm)

-

系统集成:通过PCIe/CXL互连实现异构计算

-

软件依赖:需配套编译器优化(如CUDA/TensorRT)

领域分工对比

| 计算类型 | 代表芯片 | 性能优势领域 |

|---|---|---|

| 标量计算 | CPU/MPU | 逻辑判断/系统调度 |

| 矢量计算 | GPU | 浮点运算/并行计算 |

| 张量计算 | NPU/TPU | 矩阵乘法/卷积运算 |

| 图计算 | IPU | 不规则数据流处理 |

| 序列计算 | LPU | 长文本生成/多轮对话 |

| 控制计算 | MCU | 实时信号处理 |

四、应用场景深度解析

1. 典型系统配置

-

AI服务器:CPU(任务调度)+ GPU(模型训练)+ LPU(对话生成)

-

智能汽车:MCU(车身控制)+ MPU(决策系统)+ NPU(视觉处理)

-

云数据中心:DPU(网络卸载)+ IPU(图分析)+ TPU(推荐系统)

2. 市场格局演变

-

AI芯片:NVIDIA H100 vs Google TPUv4 vs 寒武纪MLU370

-

新兴领域:Groq LPU在170B模型推理延迟<1秒

-

嵌入式市场:瑞萨MPU占据工业控制38%份额

五、未来技术演进方向

1. 架构创新

-

三维集成:台积电CoWoS封装实现CPU+LPU+HBM堆叠

-

存算一体:三星HBM-PIM在内存内完成AI运算

-

光子集成:Ayar Labs的光学I/O突破芯片互连带宽瓶颈

2. 软件定义硬件

-

可重构架构(如Tenstorrent芯片支持动态配置为GPU/NPU)

-

开源指令集(RISC-V生态出现AI扩展指令集)

3. 能效突破

-

超导芯片:IBM量子计算芯片在特定任务能效提升万倍

-

神经形态芯片:Intel Loihi模拟人脑突触能效特性

结语

从CPU的通用计算到LPU的语言智能,芯片的专用化进程印证了"软件定义硬件"的技术趋势。未来的计算架构将呈现两大特征:一方面,DPU/IPU等基础设施芯片持续优化数据中心TCO;另一方面,LPU/NPU等智能芯片推动AI应用平民化。只有理解不同芯片的特性光谱,才能构建优化的计算系统。